# **GPIB-COM** User Manual

June 1990 Edition

Part Number 320197-01

© Copyright 1989, 1991 National Instruments Corporation. All Rights Reserved.

National Instruments Corporation 6504 Bridge Point Parkway Austin, TX 78730-5039

(512) 794-0100 (800) IEEE-488 (toll-free U.S. and Canada) Technical support fax: (512) 794-5678

### Limited Warranty

The GPIB-COM is warranted against defects in materials and workmanship for a period of two years from date of shipment. National Instruments will repair or replace equipment which proves to be defective during the warranty period. This warranty includes parts and labor. A Return Material Authorization (RMA) number must be obtained from National Instruments before any equipment is returned for repair. Faults caused by misuse are not covered under the warranty. During the warranty period, the owner may return failed parts to National Instruments for repair. National Instruments will pay the shipping costs of returning the part to the owner. All items returned to National Instruments for repair must be clearly marked on the outside of the package with an RMA number.

No other warranty is expressed or implied. National Instruments shall not be liable for consequential damages. Contact National Instruments for more information.

### **Important Notice**

The material in this manual is subject to change without notice. National Instruments assumes no responsibility for errors which may appear in this manual. National Instruments makes no commitment to update, nor to keep current, the information contained in this document.

## Copyright

Under the copyright laws, this manual may not be copied, photocopied, reproduced, translated, in whole or in part, without the prior written consent of National Instruments Corporation.

### Trademark

IBM is a registered trademark of International Business Machines Corporation.

## **FCC/DOC Radio Frequency Interference Compliance**

This equipment generates and uses radio frequency energy and, if not installed and used in strict accordance with the instructions in this manual, may cause interference to radio and television reception. This equipment has been tested and found to comply with (1) the limits for a Class B computing device, in accordance with the specifications in Part 15 of U.S. Federal Communications Commission (FCC) Rules, and (2) the limits for radio noise emissions from digital apparatus set out in the Radio Interference Regulations of the Canadian Department of Communications (DOC). These regulations are designed to provide reasonable protection against interference from the equipment to radio and television reception in residential areas.

There is no guarantee that interference will not occur in a particular installation. However, the chances of interference are much less if the equipment is used according to this instruction manual.

If the equipment does cause interference to radio or television reception, which can be determined by turning the equipment on and off, one or more of the following suggestions may reduce or eliminate the problem.

- Operate the equipment and the receiver on different branches of your AC electrical system.

- Move the equipment away from the receiver with which it is interfering.

- Relocate the equipment with respect to the receiver.

- Reorient the receiver's antenna.

- Be sure that the equipment is plugged into a grounded outlet and that the grounding has not been defeated with a cheater plug.

If necessary, consult National Instruments or an experienced radio/television technician for additional suggestions. The following booklet prepared by the FCC may also be helpful: *How to Identify and Resolve Radio-TV Interference Problems*. This booklet is available from the U.S. Government Printing Office, Washington, DC 20402, Stock Number 004-000-00345-4.

# Preface

## **Introduction to the GPIB-COM**

The GPIB-COM is a high-performance talk/listen interface board that makes communication possible between IEEE-488 devices and IBM personal computers and compatibles (hereafter referred to as PCs) equipped with software that uses the serial ports.

## **Organization of This Manual**

This manual is divided into the following sections:

Section One, *Introduction*, contains a brief description of the GPIB-COM including a listing of its features, accessories, and components.

Section Two, *Configuration and Installation*, describes how to configure and install the GPIB-COM into your system.

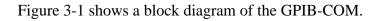

Section Three, *Function Description*, shows a block diagram of the GPIB-COM and describes the functional components of the GPIB-COM.

Section Four, *Running Diagnostic Tests*, describes how to run the diagnostic tests that are shipped with the GPIB-COM.

Section Five, *Programming the GPIB-COM*, presents a description of the GPIB-COM Serial Port Emulator registers and information on programming the IBM serial adapter.

Appendix A, Specifications, lists the specifications of the GPIB-COM board.

Appendix B, *Multiline Interface Command Messages*, contains an ASCII chart and a list of the corresponding GPIB messages.

Appendix C, *Operation of the GPIB*, describes GPIB terminology and protocol for users unfamiliar with the GPIB.

## **Related Documents**

The following documents contain information that may be helpful as you read this manual:

- ANSI/IEEE Std 488-1978, IEEE Standard Digital Interface for Programmable Instrumentation

- IBM Options and Adapters Manual

- IBM PC Technical Reference Manual

- IBM Disk Operating System Manual

- INS8250A Data Sheet, National Semiconductor

Preface

## **Abbreviations Used in This Manual**

The following abbreviations are used in the text of this manual.

| $\leq \geq \\ \geq \\ \pm \\ A \\ C \\ hex \\ in. \\ I/O \\ kbyte \\ m \\ Mbyte \\ MHz \\ msec \\ r \\ r \\ r/w \\ sec \\ V \\ VDC \\ NDC \\ $ | is less than or equal to<br>is greater than or equal to<br>plus or minus<br>ampere<br>Celsius<br>hexadecimal<br>inch<br>input/output<br>1000 bytes<br>meter<br>megabyte<br>megahertz<br>millisecond<br>read<br>read/write<br>second<br>volt |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                |                                                                                                                                                                                                                                             |

| VDC                                                                                                                                            | volts direct current                                                                                                                                                                                                                        |

| W                                                                                                                                              | write                                                                                                                                                                                                                                       |

| ٧٧                                                                                                                                             | WIIIC                                                                                                                                                                                                                                       |

# Contents

| Section One                                         |     |

|-----------------------------------------------------|-----|

| Introduction                                        | 1-1 |

| GPIB-COM Characteristics                            |     |

| What Your Kit Should Contain                        |     |

| Optional Equipment                                  | 1-3 |

| Section Two                                         |     |

| Configuration and Installation                      | 2-1 |

| Configuration                                       |     |

| Switch and Jumper Settings                          |     |

| Base I/O Address and Interrupt Selection            |     |

| Talk/Listen Modes                                   |     |

| Talk/Listen Address and Special Function Selection  |     |

| Installation                                        |     |

| Special Considerations When Using the GPIB-COM      |     |

| Section Three                                       |     |

| Function Description                                | 3-1 |

| The GPIB-COM Interface                              |     |

| GPIB-COM Components                                 |     |

| Address Decoding                                    |     |

| Configuration Jumpers                               |     |

| INS8250A Compatible Registers                       |     |

| GPIB Acceptor and Source Handshaking                |     |

| Mode Control Logic                                  |     |

| Interrupt Control Logic                             | 3-3 |

| Direction Buffers                                   | 3-4 |

| GPIB Transceivers                                   | 3-4 |

| Section Four                                        |     |

| Running Diagnostic Tests                            |     |

| The GPIB-COM Test Commands                          | 4-1 |

| -1 printer test                                     | 4-1 |

| -2 plotter test                                     |     |

| -c change COM configuration                         |     |

| -q quit                                             | 4-3 |

| Section Five                                        |     |

| Programming the GPIB-COM                            | 5-1 |

| The GPIB-COM Registers                              |     |

| Transmitter Holding Register                        |     |

| Receive Buffer Register                             |     |

| Divisor Latch Least Significant Byte (LSB) Register |     |

| Divisor Latch Most Significant Byte (MSB) Register  |     |

| Interrupt Enable Register                           |     |

| Interrupt Identification Register                   | 5-7 |

|                                                     |     |

| Line Control Register                   |      |

|-----------------------------------------|------|

| Modem Control Register                  | 5-10 |

| Line Status Register                    |      |

| Modem Status Register                   | 5-14 |

| Programming the Serial Adapter          | 5-16 |

| Polling Method                          | 5-16 |

| Interrupt-Driven Method                 | 5-16 |

| The GPIB-COM Controller Function        |      |

| Appendix A                              |      |

| Specifications                          |      |

| ~F·····                                 |      |

| Appendix B                              |      |

| Multiline Interface Command Messages    | B-1  |

| internate Command Messages              | ц. т |

| Appendix C                              |      |

| Operation of the GPIB                   | C-1  |

| History of the GPIB                     |      |

| Types of Messages                       |      |

| Talkers, Listeners, and Controllers     |      |

| System Controller and Active Controller |      |

| GPIB Signals                            |      |

| Data Lines                              | C-3  |

| Handshake Lines                         |      |

| NRFD (not ready for data)               |      |

| NDAC (not data accepted)                |      |

| DAV (data valid)                        |      |

| Interface Management Lines              |      |

| ATN (attention)                         |      |

| IFC (interface clear)                   |      |

| REN (remote enable)                     |      |

| SRQ (service request)                   |      |

| EOI (end or identify)                   |      |

| Physical and Electrical Characteristics |      |

| Configuration Restrictions              |      |

| -                                       |      |

## Figures

| Figure 1-1. | GPIB-COM Board                                                      | 1-2 |

|-------------|---------------------------------------------------------------------|-----|

|             | GPIB-COM Parts Locator Diagram                                      |     |

| Figure 2-2. | Possible Settings for GPIB-COM Jumpers                              | 2-4 |

|             | Jumper W1 Settings                                                  |     |

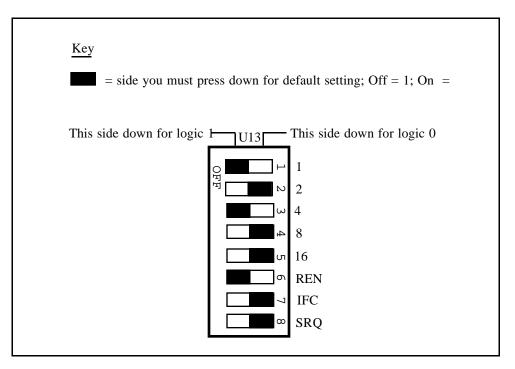

| Figure 2-4. | Switch Setting for REN* OFF, IFC* ON, SRQ* ON, and Listen Address 5 | 2-5 |

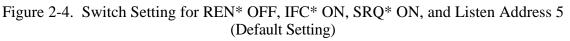

| Figure 2-5. | Listen Address Setting for Listen Address 10 Hex                    | 2-6 |

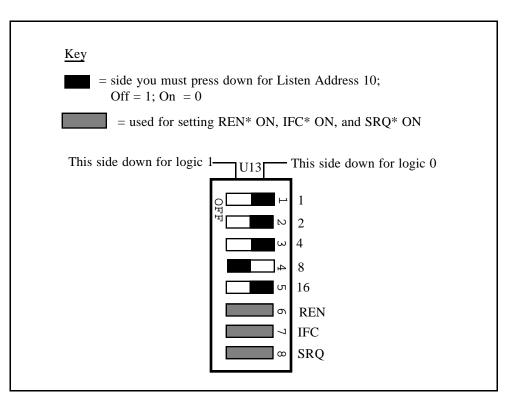

| Figure 2-6. | Switch Setting for REN* ON, IFC* OFF, and SRQ* OFF                  | 2-7 |

| Figure 3-1. | Block Diagram of GPIB-COM                                           | 3-2 |

| Figure 4-1. | Plotter Output                                                      | 4-2 |

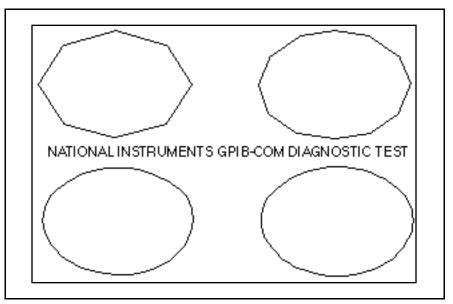

| Figure C-1. | GPIB Cable Connector                                                | C-3 |

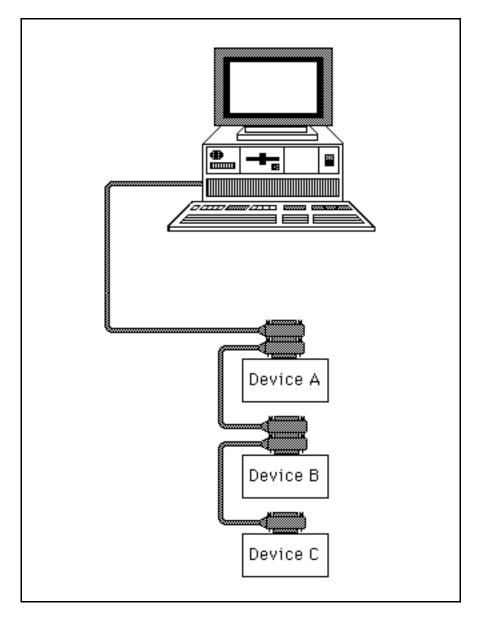

| Figure C-2. | Linear Configuration of the GPIB Devices                            | C-5 |

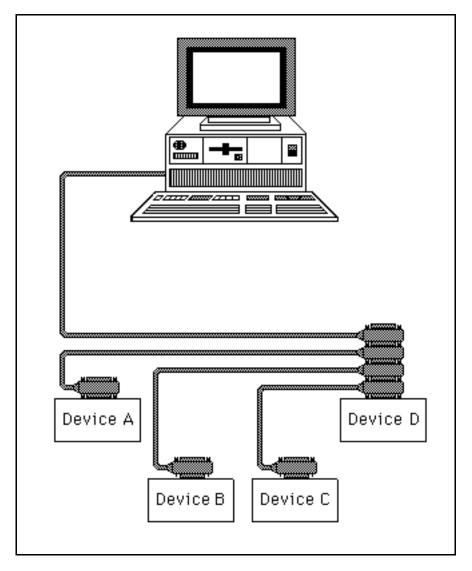

| Figure C-3. | Star Configuration of GPIB Devices                                  | C-6 |

## Tables

| Table 2-1. | IBM PC Serial Port Adapters                          | 2-3 |

|------------|------------------------------------------------------|-----|

|            | Factory Default Settings and Optional Configurations |     |

|            |                                                      |     |

| Table 5-1. | GPIB-COM Registers                                   |     |

|            | Interrupt Types and Priorities                       |     |

| Table 5-3. | Word Length Select Bits                              | 5-9 |

# Section One Introduction

This section contains a brief description of the GPIB-COM interface and a list of its characteristics and components.

## **GPIB-COM** Characteristics

The National Instruments GPIB-COM is a high-performance talk/listen interface that converts data between a standard serial port format and IEEE-488 General Purpose Interface Bus (GPIB) format for use with IEEE-488 printers and plotters. It can be used with any serial port software on the PC. The GPIB-COM looks like a standard serial port to the IBM PC operating system and software. It can be used to interface IEEE-488 devices to any PC software that uses the serial ports.

The GPIB-COM has the following hardware features:

- emulates the standard PC serial adapter interface so that no additional software is needed

- can be configured as either COM1, COM2, COM3, or COM4

- compatible with any software using the serial ports on the IBM PC and its compatibles

- transparent addressing of unaddressed Talkers and Listeners

- choice of talk-only mode for use with listen-only printers and plotters

- choice of REN mode, which operates an instrument in the remote mode

- choice of SRQ enable, which allows monitoring of asynchronous service requests

- choice of IFC mode, which sends an interface clear when the computer is powered on

Figure 1-1 shows the GPIB-COM interface board.

Figure 1-1. GPIB-COM Board

## What Your Kit Should Contain

Your kit should contain the following components:

| Item                                                                                                                                                         | Part Number |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| GPIB-COM interface board                                                                                                                                     | 180750-01   |  |

| GPIB-COM User Manual                                                                                                                                         | 320197-01   |  |

| GPIB-COM Diagnostic Test Diskette                                                                                                                            | 420212-45   |  |

| <b>Note:</b> The GPIB-COM Diagnostic Test Diskette contains the com.exe diagnostic test that is described in Section Four, <i>Running Diagnostic Tests</i> . |             |  |

Make sure each of these items is in your kit. If any item is missing, contact National Instruments.

# **Optional Equipment**

| Item                                                                                                                                                                                                                                                         | Part Number |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| Double-Shielded Cables:                                                                                                                                                                                                                                      |             |  |

| GPIB Type X2 Cable - 1 m                                                                                                                                                                                                                                     | 763061-01   |  |

| GPIB Type X2 Cable - 2 m                                                                                                                                                                                                                                     | 763061-02   |  |

| GPIB Type X2 Cable - 4 m                                                                                                                                                                                                                                     | 763061-03   |  |

| <ul> <li>In order to meet FCC emission limits for a Class B device, you must use a shielded<br/>GPIB cable. Operating this equipment with a non-shielded cable may cause interference<br/>to radio and television reception in residential areas.</li> </ul> |             |  |

# Section Two Configuration and Installation

This section contains information on how to configure and install the GPIB-COM into your system.

## Configuration

Figure 2-1 shows the locations of the GPIB-COM configuration jumpers and switches.

| V1 U2                                  |                                                 |

|----------------------------------------|-------------------------------------------------|

|                                        | U3 U4 U12 U5                                    |

| Z<br>) 8 2 LS74 8 2 LS273              | ] [♣] LS147 [] LS174 [] € LS244 [] BSWITCH []   |

| U8 C44 U9                              |                                                 |

| រឹកដ្ឋ LS123 🗗 701008                  | ] [] LS11 ] [] > LS244 ] [] LS244 ] [] [] LS240 |

|                                        |                                                 |

| B LS123 10 701009                      | [ \$ LS08 \$ 5 LS273 \$ LS244 \$ 75160 (        |

|                                        |                                                 |

|                                        |                                                 |

|                                        | [] LS74 0 LS374 1 LS244 1 ALS576 J1             |

|                                        |                                                 |

| SPARE DEST                             | D LS138 LS374 D LS244 D ALS576                  |

| U44 U32 U33                            | U34 U35 @@ 000 U37                              |

| SPARE D LS04 D LS32                    | C LS138 LS30 LS240 LS245                        |

| U45 U38 U39<br>COP/RIGHT © 1989 ASSY16 | U40 U41 U42 U43 C48                             |

| CUARIGHT @ 1989 H33118                 | 30750-01 REU.B C47 CT \$ #8 # C C48             |

|                                        |                                                 |

| ∠ Talk/Listen Modes                    | Base Address and J Talk/Listen Address J        |

|                                        | Interrupt Selection and Special Function        |

Figure 2-1. GPIB-COM Parts Locator Diagram

When installing the GPIB-COM you must determine which serial port the GPIB-COM board will respond to and select the appropriate base address and interrupt level. The GPIB-COM can be configured to one of four base addresses:

- 3F8 for Serial Port 1

- 2F8 for Serial Port 2

- 3E8 for Serial Port 3

- 2E8 for Serial Port 4

Note: DOS and BIOS only recognize base addresses 3F8 and 2F8.

The GPIB-COM is shipped from the factory set to 3F8. It must be reconfigured to another base address if another device (such as a printer adapter card or a built-in serial port) is already at that address.

DOS has reserved device names for the serial ports it finds in the system: COM1 and COM2. The serial port adapters are named in the order in which they are found. When the computer is powered on, DOS searches the serial port addresses for installed adapters. It first searches 3F8, then 2F8. If only one device is installed, that device is named COM1 regardless of what its I/O address is. If there is more than one serial device installed, the first one found is assigned COM1 and the second one found is assigned COM2.

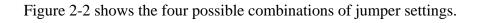

Some communications software also recognizes COM3 (base address 3E8) and COM4 (base address 2E8). If you wish to use COM3 or COM4, set the jumpers to the desired base address as shown in Figure 2-2. DOS and BIOS do not recognize COM3 or COM4. Consult your software documentation to see which interrupt level, if any, is required. If interrupts are not used, the jumper can be removed or stored with only one side on a pin.

The GPIB-COM may need to be reconfigured if its interrupt level conflicts with another device. If the base I/O address of the GPIB-COM does not conflict with any other device in your computer and the GPIB-COM still does not work with your software package, reconfigure the GPIB-COM to a different interrupt level.

Table 2-1 shows the standard base I/O address and interrupt level for each serial port.

| Name of Port  | Base I/O Address (hex) | Interrupt Level |

|---------------|------------------------|-----------------|

| Serial Port 1 | 3F8                    | 4               |

| Serial Port 2 | 2F8                    | 3               |

| Serial Port 3 | 3E8                    | Not Used        |

| Serial Port 4 | 2E8                    | Not Used        |

Table 2-1. IBM PC Serial Port Adapters

#### Switch and Jumper Settings

Table 2-2 shows the factory settings and optional configurations for the switches and jumpers on the GPIB-COM.

| Table 2-2.  | Factory Default  | Settings and Or | otional Configurations |

|-------------|------------------|-----------------|------------------------|

| 1 4010 2 2. | I dotory Dordant | settings and Op | Stional Configurations |

| GPIB-COM         | Default | Optional      |  |

|------------------|---------|---------------|--|

| Base I/O Address | 3F8     | 2F8, 3E8, 2E8 |  |

| Interrupt Level  | 4       | 3             |  |

If you need to change the factory settings, continue on. If you do not need to change the factory settings, skip to *Installation* later in this section.

### **Base I/O Address and Interrupt Selection**

The base I/O address and interrupt line used by the GPIB-COM are determined by the jumpers located at positions W2 and W5. The jumpers are set at the factory for base I/O address 3F8 hex and interrupt level 4.

Figure 2-2. Possible Settings for GPIB-COM Jumpers

#### Talk/Listen Modes

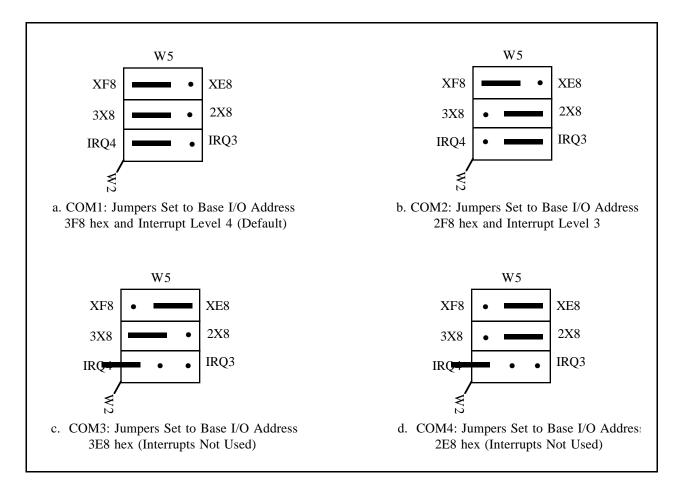

If you are using your GPIB-COM with a listen-only printer or plotter, you can configure the GPIB-COM for a talk-only mode. In this mode, the GPIB-COM is always a Talker and never sends any interface commands. To set the talk-only mode, change jumper W1 from T/L to T as shown in Figure 2-3:

Figure 2-3. Jumper W1 Settings

#### Talk/Listen Address and Special Function Selection

The GPIB-COM interface board has eight onboard DIP switches you can use to configure the GPIB controller responsibilities. In the talk/listen mode, the first five switches set the talk or listen address of the external device(s) that will be attached to the GPIB-COM. In the talk-only mode, the GPIB-COM does not send a talk or listen address.

The three remaining switches (REN, IFC, and SRQ) have the following special functions:

Note: An asterisk (\*) after a signal name indicates that the signal is inverted (negative logic).

- REN\* Asserts/unasserts the Remote Enable (REN) line that places an instrument in remote mode. The ON position enables REN. The OFF position disables REN.

- IFC\* Enables/disables the Interface Clear (IFC) option on the GPIB-COM. If enabled, the GPIB-COM issues an IFC when it is initialized. The ON position enables IFC on initialization. The OFF position holds IFC unasserted.

- SRQ\* Enables/disables the Service Request (SRQ) option. If enabled, the GPIB-COM monitors the SRQ line through the Parity Error Bit (PE) in the Line Status Register. When the switch is ON, the PE bit reflects the status of the SRQ line. When the switch is OFF, the PE bit is always clear.

The GPIB-COM factory default switch configuration is for device listen address 5, REN\* not asserted, IFC\* enabled, and SRQ\* enabled. Figure 2-4 shows the factory default switch settings for the GPIB-COM.

Figure 2-5 shows the switch configuration needed when using a device with listen address 10 hex. The listen address varies with each device so check the listen address of your device and set these five bits accordingly.

Figure 2-5. Listen Address Setting for Listen Address 10 Hex

Figure 2-6 shows the switch configuration for REN\* asserted, IFC\* disabled, and SRQ\* disabled.

Figure 2-6. Switch Setting for REN\* ON, IFC\* OFF, and SRQ\* OFF

## Installation

Once you have changed, verified, and recorded the switches and jumper settings, you are ready to install the GPIB-COM.

The following steps are general installation instructions. Consult the user manual or technical reference manual of your personal computer for specific instructions and warnings.

- 1. Turn off your computer.

- 2. Remove the plug from its power source.

- 3. Remove the top cover or access port to the I/O channel.

- 4. Remove the expansion slot cover on the back panel of your computer.

- 5. Insert the GPIB-COM in an unused full-length slot with the IEEE-488 receptacle sticking out of the opening of the back panel. It may be a tight fit, but do not force the board into place.

- 6. Screw the right angle mounting bracket of the GPIB-COM to the back panel rail of your computer.

- 7. Check the installation.

- 8. Replace the expansion slot cover of your computer.

- 9. Connect the GPIB cable to the GPIB-COM.

## **Special Considerations When Using the GPIB-COM**

The GPIB-COM does not support XON/XOFF protocols. If your application software uses XON/XOFF protocols, send your printer and plotter output to a file on disk. From DOS, send your file to the GPIB-COM by using the DOS command:

copy filename COM1:

copy filename COM2:

The DOS MODE command is used to set the RS-232 parameters that will be used when COM1 and COM2 are accessed through DOS. Sometimes a timeout error may occur when writing through the GPIB-COM to a slow device such as a printer or a plotter. If this happens, use the MODE command to disable the timeout function by typing MODE COM1:12,,,,P. Some software applications use the COM port baud rate setting to control the data transmission speed. To obtain the fastest possible transfer rates, set the baud rate setting to 9600 baud. The P at the end disables the timeout. For more information on the MODE command, refer to the *IBM Disk Operating System Manual*. This command can also be used in an autoexec.bat file to disable timeouts when you start up the computer.

# Section Three Function Description

This section contains a block diagram of the GPIB-COM, followed by a description of each of its functional components.

## The GPIB-COM Interface

The GPIB-COM is a completely transparent interface between GPIB devices and any IBM PC software that uses serial ports. A set of I/O registers identical to those on the standard IBM serial adapter is used. On the GPIB side, the GPIB-COM includes a limited subset of interface functions that address a GPIB device to listen when the computer sends data to the serial port and to talk when the computer is waiting to receive data from the serial port. In order to be able to respond immediately to commands and data sent to the serial port, the GPIB-COM must be the GPIB System Controller and cannot work with other Controllers present.

Figure 3-1. Block Diagram of GPIB-COM

## **GPIB-COM** Components

The interface consists of the following functional components:

- Address Decoding

- Configuration Jumpers

- INS8250A Compatible Registers

- GPIB Acceptor and Source Handshaking

- Mode Control Logic

- Interrupt Control Logic

- Direction Buffers

- GPIB Transceivers

#### **Address Decoding**

Address decoding monitors the PC address bus to recognize when a GPIB-COM address is present and enables a read and/or write to its registers.

#### **Configuration Jumpers**

These onboard jumpers select the base address, GPIB controller mode, and interrupt request line used by the GPIB-COM.

#### **INS8250A** Compatible Registers

The main component of an IBM PC compatible serial adapter is an INS8250A Asynchronous Communications chip or its equivalent, which handles RS-232 communication. The INS8250A compatible registers on the GPIB-COM emulate the serial adapter registers so that the GPIB-COM will operate transparently with any serial port driver.

#### **GPIB** Acceptor and Source Handshaking

This circuitry converts PC serial port handshaking into GPIB handshaking. This process is completely software-transparent.

#### **Mode Control Logic**

This circuitry determines whether the GPIB-COM should be a Talker (and the target device a Listener) or a Listener (and the target device a Talker).

#### **Interrupt Control Logic**

This circuitry generates and masks interrupts on GPIB conditions which correspond to the conditions that would cause the INS8250A circuit to generate an interrupt.

### **Direction Buffers**

These buffers control the direction in which data information travels.

#### **GPIB** Transceivers

The GPIB-COM is interfaced to the IEEE-488 bus by National Semiconductor 75160A and 75162A transceivers. These integrated circuits are specifically designed to provide power-up/power-down bus protection (glitch-free). The GPIB-COM counts as one IEEE-488 bus load, thereby allowing an additional 14 devices to be connected before exceeding the bus loading restrictions imposed by the IEEE-488.

# Section Four Running Diagnostic Tests

### The GPIB-COM Test Commands

The GPIB-COM Diagnostic Tests can be used to verify the configuration of the GPIB-COM and its connection to a GPIB printer or plotter.

To run a GPIB-COM diagnostic test, connect a printer or plotter to the GPIB and run the program com.exe from the GPIB-COM diagnostic test diskette. The following message will appear on the screen:

NATIONAL INSTRUMENTS GPIB-COM DIAGNOSTIC TESTS

This program assumes the GPIB-COM is configured at base address 3F8 (COM1).

If you reconfigured your GPIB-COM you must change the address that this program uses. To do this, enter command c from the menu.

Enter one of the following commands:

- -1 printer test

- -2 plotter test

- -c change COM configuration

- -q quit

- ?

A short explanation of each command is given in the following paragraphs.

#### -1 printer test

Select this test to verify the configuration of the GPIB-COM when connecting it to a GPIB ASCII printer. This test will send characters to the printer.

Entering this command returns the prompt:

Starting printer test. Press any key to stop printing. The printer should begin printing a string of characters. To stop the test, press any key. The following message then appears:

```

Printer test finished.

Please check output to printer with user manual instructions.

```

The output on the printer should read:

```

NATIONAL INSTRUMENTS GPIB-COM DIAGNOSTIC TEST!"#$%&'()*+,-.

/0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[\]_'abcdefghijkl

mnopqrstuvwxyz{|}~ !"#$%&'()*+,./0123456789:;<=>?@ABCDEFGHI

JKLMNOPQRSTUVWXY Z[\]_'abcdefghijklmnopqrstuvwxyz{|}~ !"#$%&'

()*+,./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[\]_'abcdefghi

jklmnopqrstuvwxyz{|}~ !"#$%&'()*+,./0123456789:;<=>?@ABCDEFG

HIJKLMNOPQRSTUVWXYZ[\]_'abcdefghijklmnopqrstuvwxyz{|}~

```

If the printer does not respond, an error message appears on the screen along with a message telling you to recheck all of your connections and jumper settings. If the test still fails after everything has been checked, write down the error message, if any, and call National Instruments.

### -2 plotter test

Select this test to verify the configuration of the GPIB-COM when connecting it to a GPIB HP-GL plotter. This test will send output to the plotter.

When this command is selected, the computer prints the following message:

Starting plotter test.

As illustrated in Figure 4-1, the plotter begins to draw four ovals.

Figure 4-1. Plotter Output

When it is finished, the following message appears on the screen:

Plotter test finished. Please check output to plotter with user manual instructions.

If the plotter does not respond or the output on the plotter does not match Figure 4-1, check again to be sure that all of the connections are tight and the jumpers are all set correctly. Try the test again. If it still does not work, write down any error messages that appear and call National Instruments.

#### -c change COM configuration

This command is used to change the base address of the GPIB-COM to match the actual board settings. If you have changed the jumper settings to something different than the default settings, you must run this command.

When this command is selected, the following menu appears:

```

This program assumes the GPIB-COM is configured at base address

3F8 (COM1).

Enter the number of the correct address.

1) base address 3F8 (COM1)

2) base address 2F8 (COM2)

Enter 1, 2, or <return> for no change?

```

Type in the number of the address that you have configured the board to. The computer prints out your choice and returns to the main menu.

#### -q quit

This command ends the test program and returns to DOS.

# Section Five Programming the GPIB-COM

This section presents a description of the GPIB-COM Serial Port Emulator registers and information on programming the GPIB-COM. You need to use this section only if you are writing your own serial port device driver.

## The GPIB-COM Registers

IBM's serial adapter is a plug-in card for the PC that handles RS-232 communication. The main component of the adapter is an INS8250 Asynchronous Communications chip or its equivalent, which is controlled by programming a set of registers on the I/O channel. The names of these registers and their I/O addresses are given in Table 5-1. Each register is located at a certain offset from the base address of the board. The addresses are given with an *X* for the first digit and a *Y* for the second digit, where XY=3F for COM1 (base address 3F8), XY=2F for COM2 (base address 2F8), XY=3E for COM3 (base address 3E8), and XY=2E for COM4 (base address 2E8). Notice that sometimes two registers share the same I/O address. The DLAB bit (bit 7 of the Line Control Register) determines which register will respond when these addresses are accessed.

**Note:** Throughout this section, the term *set* will be used to mean that a bit is a logical 1, and *clear* will mean that the bit is a logical 0.

| Register                                                                                                                                                                                                                                                                                  | Туре                                                                                                      | I/O Address<br>XY=3F for COM1<br>XY=2F for COM2<br>XY=3E for COM3<br>XY=2E for COM4                             | Offset from<br>Base Address                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Transmitter Holding Register<br>Receive Buffer Register<br>Divisor Latch LSB Register<br>Divisor Latch MSB Register<br>Interrupt Enable Register<br>Interrupt Identification Register<br>Line Control Register<br>Modem Control Register<br>Line Status Register<br>Modem Status Register | write<br>read/write<br>read/write<br>read/write<br>read/write<br>read/write<br>read/write<br>read<br>read | XY8 (DLAB=0)<br>XY8 (DLAB=0)<br>XY8 (DLAB=1)<br>XY9 (DLAB=1)<br>XY9 (DLAB=0)<br>XYA<br>XYB<br>XYC<br>XYD<br>XYE | $ \begin{array}{c} 0 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 6 \end{array} $ |

Table 5-1. GPIB-COM Registers

The following pages describe the functions of each register on the serial adapter and on the GPIB-COM. For a more complete description of the serial adapter, refer to the *IBM Options and Adapters Manual*.

#### **Transmitter Holding Register**

Offset from Base I/O Address = 0

Register Address = XF8

DLAB bit in Line Control Register = 0

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|    |    |    |    |    |    |    | W  |

The Transmitter Holding Register contains the character to be sent to the serial output, with bit 0 being the least significant and bit 7 the most significant. It functions identically on the GPIB-COM and the INS8250.

| Bit  | Mnemonic | Description           |  |  |

|------|----------|-----------------------|--|--|

| 7-0w | D[7-0]   | Data Bits 7 through 0 |  |  |

#### **Receive Buffer Register**

Offset from Base I/O Address = 0

Register Address = XF8

DLAB bit in Line Control Register = 0

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0 R |

|----|----|----|----|----|----|----|-----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

The Receive Buffer Register contains the character received from the serial input, with bit 0 being the least significant and bit 7 the most significant. It functions identically on the GPIB-COM and the INS8250.

| Bit  | Mnemonic | Description           |  |  |

|------|----------|-----------------------|--|--|

| 7-0r | D[7-0]   | Data Bits 7 through 0 |  |  |

#### Divisor Latch Least Significant Byte (LSB) Register

Offset from Base I/O Address = 0

Register Address = XF8

DLAB bit in Line Control Register = 1

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| DL7 | DL6 | DL5 | DL4 | DL3 | DL2 | DL1 | DL0 | R/W |

| Bit    | Mnemonic | Description           |

|--------|----------|-----------------------|

| 7-0r/w | DL[7-0]  | Data Bits 7 through 0 |

#### Divisor Latch Most Significant Byte (MSB) Register

Offset from Base I/O Address = 1

Register Address = XF9

DLAB bit in Line Control Register = 1

| 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   | _   |

|------|------|------|------|------|------|-----|-----|-----|

| DL15 | DL14 | DL13 | DL12 | DL11 | DL10 | DL9 | DL8 | R/W |

The value stored in these two registers is used to determine the baud rate for serial communications. The 16-bit number formed by the Divisor Latch LSB and MSB is divided into a 1.8432 MHz clock to produce the baud rate.

The Divisor Latch Registers are ignored by the GPIB-COM circuitry; however, they are available on the GPIB-COM and can be written to and read by software.

| Bit    | Mnemonic | Description            |

|--------|----------|------------------------|

| 7-0r/w | DL[15-8] | Data Bits 15 through 8 |

#### **Interrupt Enable Register**

Offset from Base I/O Address = 1

Register Address = XF9

DLAB bit in Line Control Register = 0

| 7 | 6 | 5 | 4 | 3  | 2   | 1   | 0   | _   |

|---|---|---|---|----|-----|-----|-----|-----|

| 0 | 0 | 0 | 0 | MS | RLS | THR | RDA | R/W |

The Interrupt Enable Register is a read/write register that allows the programmer to selectively enable or disable each of the four possible types of interrupts generated by the INS8250. The high four bits are not used and are permanently cleared. The lower four bits each enable one type of interrupt as listed below.

| Bit    | Mnemonic | Description                                                                                                                                                                                              |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4r/w | 0        | Reserved Bits 7 through 4                                                                                                                                                                                |

|        |          | These bits always read as 0.                                                                                                                                                                             |

| 3r/w   | MS       | Modem Status Interrupt Enable Bit                                                                                                                                                                        |

|        |          | This bit enables a modem status interrupt when set to logical 1.<br>The modem status interrupt occurs when any of bits 0 through 3<br>of the Modem Status Register are set to logical 1.                 |

|        |          | This bit is identical on the GPIB-COM and the INS8250, but<br>bits 0 through 3 of the Modem Status Register are set for<br>different conditions as noted under the Modem Status Register<br>description. |

| 2r/w   | RLS      | Receive Line Status Interrupt Enable Bit                                                                                                                                                                 |

|        |          | This bit enables a line status interrupt when set. The line status interrupt occurs when any of bits 1 through 4 of the Line Status Register become set.                                                 |

|        |          | This bit is identical on the GPIB-COM and the INS8250, but<br>bits 1 through 4 of the Line Status Register are set for different<br>conditions as noted under the Line Status Register description.      |

| Bit  | Mnemonic | Description                                                                                                                                                                                               |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1r/w | THR      | Transmitter Holding Register Interrupt Enable Bit                                                                                                                                                         |

|      |          | This bit enables a transmitter holding register empty interrupt<br>when set. The transmitter holding register empty interrupt<br>occurs when the INS8250 becomes ready to send another<br>character.      |

|      |          | This bit functions identically on the GPIB-COM and the INS8250.                                                                                                                                           |

| 0r/w | RDA      | Received Data Available Interrupt Enable Bit                                                                                                                                                              |

|      |          | This bit enables a received data available interrupt when set. The received data available interrupt occurs when a character is received from the serial input and stored in the Receive Buffer Register. |

|      |          | This bit functions identically on the GPIB-COM and the INS8250.                                                                                                                                           |

#### **Interrupt Identification Register**

Offset from Base I/O Address = 2

Register Address = XFA

| 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0 R |

|---|---|---|---|---|-----|-----|-----|

| 0 | 0 | 0 | 0 | 0 | ID1 | ID0 | INT |

The Interrupt Identification Register is a read-only register which tells you when an interrupt is pending and if so, what kind of interrupt it is. This register functions identically on the GPIB-COM and the INS8250.

| Bit  | Mnemonic | Description                                                                                                                                                                                          |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3r | 0        | Reserved Bits 7 through 3                                                                                                                                                                            |

|      |          | These bits always read as 0.                                                                                                                                                                         |

| 2-1r | ID[1-0]  | Identify Interrupt Register Bits                                                                                                                                                                     |

|      |          | These two bits identify the interrupt that is pending. If more than one interrupt is pending, only the one with the highest priority is identified. The types and priorities are given in Table 5-2. |

| Table 5-2. | Interrupt | Types | and | Priorities |

|------------|-----------|-------|-----|------------|

|------------|-----------|-------|-----|------------|

| Bit 2       | Bit 1                                      | Type of Interrupt                                                      | Priority   |

|-------------|--------------------------------------------|------------------------------------------------------------------------|------------|

| 0<br>0<br>1 | $\begin{array}{c} 0 \\ 1 \\ 0 \end{array}$ | Receiver Line Status<br>Received Data Available<br>Transmitter Holding | 1st<br>2nd |

| 1           | 1                                          | Register Empty<br>Modem Status                                         | 3rd<br>4th |

```

0r

```

INT

**Interrupt Pending Bit**

This bit is clear if an interrupt is pending. If set, no interrupt is pending.

### Line Control Register

Offset from Base I/O Address = 3

Register Address = XFB

| 7    | 6    | 5   | 4    | 3   | 2   | 1   | 0   |     |

|------|------|-----|------|-----|-----|-----|-----|-----|

| DLAB | SBRK | STP | EVEN | PEN | STB | WL1 | WL0 | R/W |

The Line Control Register is a read/write register that allows the programmer to set the RS-232 parameters for the INS8250. The function of each bit in this register is explained below.

| Bit  | Mnemonic | Description                                                                                                                                                                                                                                                   |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7r/w | DLAB     | Divisor Latch Access Bit                                                                                                                                                                                                                                      |

|      |          | This bit controls which registers will respond to I/O addresses XF8 and XF9. This bit is set to access the Divisor Latch LSB and MSB, and cleared to access the Transmitter Holding Register, the Receive Buffer Register, and the Interrupt Enable Register. |

|      |          | This bit functions identically on the GPIB-COM and the INS8250.                                                                                                                                                                                               |

| 6r/w | SBRK     | Set Break Control Bit                                                                                                                                                                                                                                         |

|      |          | When set, this bit causes the SOUT line of the serial cable to be forced to a logical 0 state.                                                                                                                                                                |

|      |          | This bit is ignored by the GPIB-COM.                                                                                                                                                                                                                          |

| 5r/w | STP      | Stick Parity Bit                                                                                                                                                                                                                                              |

|      |          | When this bit is set, the parity bit transmitted and detected will<br>be the inverse of the EVEN bit (bit 4), regardless of the number<br>of 1's in the data word.                                                                                            |

|      |          | This bit is ignored by the GPIB-COM.                                                                                                                                                                                                                          |

| 4r/w | EVEN     | Even Parity Select Bit                                                                                                                                                                                                                                        |

|      |          | If this bit is set, even parity will be generated and checked. If<br>this bit is clear, odd parity will be generated and checked.                                                                                                                             |

|      |          | This bit is ignored by the GPIB-COM.                                                                                                                                                                                                                          |

|      |          |                                                                                                                                                                                                                                                               |

| Bit    | Mnemonic | Description                                                                                                                                                                                               |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3r/w   | PEN      | Parity Enable Bit                                                                                                                                                                                         |

|        |          | If this bit is set, the INS8250 will generate and check parity according to the values of the STP and EVEN bits (bits 4 and 5). If this bit is clear, the INS8250 will not generate or check parity bits. |

|        |          | This bit is ignored by the GPIB-COM.                                                                                                                                                                      |

| 2r/w   | STB      | Stop Bit Control Bit                                                                                                                                                                                      |

|        |          | This bit controls the number of stop bits sent and verified by the INS8250. If this bit is set, two stop bits will be used. If this bit is clear, one stop bit will be used.                              |

|        |          | This bit is ignored by the GPIB-COM.                                                                                                                                                                      |

| 1-0r/w | WL[1-0]  | Word Length Select Bits                                                                                                                                                                                   |

|        |          | These two bits set the length of the words sent or received according to Table 5-3.                                                                                                                       |

| Table 5-3. | Word Length Select Bits   |

|------------|---------------------------|

| 14010 5 5. | tt ofa Lengui Seleet Bits |

| Bit 1 | Bit 0 | Word Length |  |

|-------|-------|-------------|--|

| 0     | 0     | 5 bits      |  |

| 0     | 1     | 6 bits      |  |

| 1     | 0     | 7 bits      |  |

| 1     | 1     | 8 bits      |  |

These bits have no meaning on the GPIB and are ignored by the GPIB-COM circuitry.

#### Modem Control Register

Offset from Base I/O Address = 4

Register Address = XFC

| 7 | 6 | 5 | 4    | 3    | 2    | 1   | 0   | _   |

|---|---|---|------|------|------|-----|-----|-----|

| C | 0 | 0 | LOOP | OUT2 | OUT1 | RTS | DTR | R/W |

The Modem Control Register is a read/write register that controls RS-232 output lines for communication with a modem or modem emulator. The function of each bit in this register is explained below.

| Bit    | Mnemonic | Description                                                                                                                                                                         |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5r/w | 0        | Reserved Bits 7 through 5                                                                                                                                                           |

|        |          | These bits always read as 0.                                                                                                                                                        |

| 4r/w   | LOOP     | Loopback Diagnostic Test Bit                                                                                                                                                        |

|        |          | When set, this bit internally connects the outputs of the INS8250 back to the inputs to allow the chip to be tested by writing data to itself and reading it back for verification. |

|        |          | This bit is ignored by the GPIB-COM circuitry.                                                                                                                                      |

| 3r/w   | OUT2     | Auxiliary Output 2 Bit                                                                                                                                                              |

|        |          | The OUT2 serial port output is the inverse of this bit. All interrupts from the serial adapter are disabled when this bit is cleared.                                               |

|        |          | When this bit is cleared, interrupts are disabled on the GPIB-COM.                                                                                                                  |

| 2r/w   | OUT1     | Auxiliary Output 1 Bit                                                                                                                                                              |

|        |          | The OUT1 serial port output is the inverse of this bit.                                                                                                                             |

|        |          | This bit is ignored by the GPIB-COM circuitry.                                                                                                                                      |

| 1r/w   | RTS      | Request to Send Bit                                                                                                                                                                 |

|        |          | The RTS serial port output is the inverse of this bit. When this bit is set, it indicates that the Controller is ready to send data.                                                |

|        |          | On the GPIB-COM, this bit is used along with the DTR bit to control the CTS bit of the Modem Status Register.                                                                       |

|        |          |                                                                                                                                                                                     |

| Bit  | Mnemonic | Description                                                                                                         |

|------|----------|---------------------------------------------------------------------------------------------------------------------|

| 0r/w | DTR      | Data Terminal Ready Bit                                                                                             |

|      |          | The DTR serial port output is the inverse of this bit. This bit is set when the Controller is ready to communicate. |

|      |          | On the GPIB-COM, this bit is used along with the RTS bit to control the CTS bit of the Modem Status Register.       |

#### Line Status Register

Offset from Base I/O Address = 5

Register Address = XFD

| 7 | 6    | 5    | 4  | 3  | 2  | 1  | 0 R |

|---|------|------|----|----|----|----|-----|

| 0 | TEMT | THRE | BI | FE | PE | OE | DR  |

The Line Status Register provides information about the status of the data transfer. On the GPIB-COM this register is implemented as a read-only register. Writing to the line status register will not change its contents. The function of each bit in this register is explained below.

| Bit | Mnemonic | Description                                                                                                                                                                                                                             |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7r  | 0        | Reserved Bit                                                                                                                                                                                                                            |

|     |          | This bit always reads as 0.                                                                                                                                                                                                             |

| бr  | TEMT     | Transmitter Shift Register Empty Bit                                                                                                                                                                                                    |

|     |          | This bit is cleared when a character is transferred from the<br>Transmitter Holding Register to the Transmitter Shift Register<br>and set when the character has been shifted out of the Shift<br>Register onto the serial output line. |

|     |          | On the GPIB-COM, there is no shift register so this bit behaves exactly the same as the THRE bit.                                                                                                                                       |

| 5r  | THRE     | Transmitter Holding Register Empty Bit                                                                                                                                                                                                  |

|     |          | This bit is cleared when the processor writes a character into the<br>Transmitter Holding Register and set when the character has<br>been transmitted and the INS8250 is ready to send another<br>character.                            |

|     |          | This bit functions identically on the GPIB-COM and the INS8250.                                                                                                                                                                         |

| 4r  | BI       | Break Interrupt Bit                                                                                                                                                                                                                     |

|     |          | This bit is set to logical 1 when the serial data input remains in<br>the logical 0 state for longer than one full word transmission<br>time.                                                                                           |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                                                                                                              |

|     |          |                                                                                                                                                                                                                                         |

| Bit | Mnemonic | Description                                                                                                                                                                                                                                                                        |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3r  | FE       | Framing Error Bit                                                                                                                                                                                                                                                                  |

|     |          | This bit is set when the received character does not have a valid stop bit.                                                                                                                                                                                                        |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                                                                                                                                                         |

| 2r  | PE       | Parity Error Bit                                                                                                                                                                                                                                                                   |

|     |          | This bit is set when the received character does not have the correct parity. It is cleared when the processor reads the Line Status Register.                                                                                                                                     |

|     |          | On the GPIB-COM, this bit is set when the SRQ* line of the GPIB is asserted. When the special function selection DIP switch has been set to disable the SRQ feature, this bit is always clear.                                                                                     |

| 1r  | OE       | Overrun Error Bit                                                                                                                                                                                                                                                                  |

|     |          | This bit is set when a new character is received and stored in the<br>Receive Buffer Register before the processor reads the previous<br>character, thus overwriting and destroying the previous<br>character. It is cleared when the processor reads the Line Status<br>Register. |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                                                                                                                                                         |

| 0r  | DR       | Data Ready Bit                                                                                                                                                                                                                                                                     |

|     |          | This bit is set when a character has been received and stored in<br>the Receive Buffer Register. It is cleared when the processor<br>reads the Receive Buffer Register.                                                                                                            |

|     |          | This bit functions identically on the GPIB-COM and the INS8250.                                                                                                                                                                                                                    |

#### Modem Status Register

Offset from Base I/O Address = 6

Register Address = XFE

| 7   | 6  | 5   | 4   | 3    | 2    | 1    | 0 R  |

|-----|----|-----|-----|------|------|------|------|

| DCD | RI | DSR | CTS | DDCD | TERI | DDSR | DCTS |

The Modem Status Register gives the state of the modem control lines and tells whether any of these lines have changed state since the register was last read. This register is read only on the GPIB-COM. Writing to this register will not change its contents. The function of each bit in this register is explained below.

| Bit | Mnemonic | Description                                                                                                                               |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7r  | DCD      | Data Carrier Detect Bit                                                                                                                   |

|     |          | This bit reflects the inverse of the serial port DCD input signal.                                                                        |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                |

| бr  | RI       | Ring Indicator Bit                                                                                                                        |

|     |          | This bit reflects the inverse of the serial port RI input signal.                                                                         |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                |

| 5r  | DSR      | Data Set Ready Bit                                                                                                                        |

|     |          | This bit reflects the inverse of the serial port DSR input signal.                                                                        |

|     |          | On the GPIB-COM, this bit is always set to indicate that the interface is ready to transfer data.                                         |

| 4r  | CTS      | Clear to Send Bit                                                                                                                         |

|     |          | This bit reflects the inverse of the serial port CTS input signal.                                                                        |

|     |          | On the GPIB-COM, this bit is the logical AND of the DTR and RTS bits of the Modem Control Register.                                       |

| 3r  | DDCD     | Delta Data Carrier Detect Bit                                                                                                             |

|     |          | This bit is set when the serial port DCD input signal changes<br>state and cleared when the processor reads the Modem Status<br>Register. |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                |

| Bit | Mnemonic | Description                                                                                                                                                        |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2r  | TERI     | Trailing Edge Ring Indicator Bit                                                                                                                                   |

|     |          | This bit is set when the serial port RI input signal changes from<br>a logical 1 to a logical 0 and cleared when the processor reads<br>the Modem Status Register. |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                                         |

| 1r  | DDSR     | Delta Set Ready Bit                                                                                                                                                |

|     |          | This bit is set when the serial port DSR input signal changes<br>state and cleared when the processor reads the Modem Status<br>Register.                          |

|     |          | On the GPIB-COM, this bit is always clear.                                                                                                                         |

| Or  | DCTS     | Delta Clear to Send Bit                                                                                                                                            |

|     |          | This bit is set when the CTS input changes state and cleared<br>when the processor reads the Modem Status Register.                                                |

|     |          | On the GPIB-COM, this bit is the logical AND of the DTR and RTS bits of the Modem Control Register.                                                                |

### **Programming the Serial Adapter**

The operation of the serial adapter is controlled by software, either IBM BIOS or an application. To transfer data to and from the serial port, the communications parameters must first be set up in the following manner:

- 1. Load the baud rate divisor into the divisor latch.

- 2. Store the RS-232 parameters in the Line Control Register.

- 3. Send the modem control signals by writing to the Modem Control Register.

- 4. Enable interrupts, if used, by writing to the appropriate bits in the Interrupt Enable Register.

Once the control registers have been programmed correctly, the software can transmit and receive serial data by polling, interrupts, or both.

#### **Polling Method**

In the polled method of operation, the Line Status Register is continuously read to check if the Data Ready Bit is set. When this bit becomes set, the Receive Buffer Register is read to get the character that just came from the serial port, and the process continues. To transmit data, the Line Status Register is polled until the Transmitter Holding Register Empty Bit is set. A byte can then be written to the Transmitter Holding Register, and polling continues.

#### **Interrupt-Driven Method**

In the interrupt-driven mode of operation, the desired interrupts are enabled through the OUT2 bit and the Interrupt Enable Register. An interrupt handler is installed to respond when an interrupt occurs. Software processes can perform other tasks until an interrupt is received. When an interrupt occurs, the handler reads the Interrupt Identification Register to determine the type of interrupt and takes appropriate action, such as reading the Receive Buffer Register in the case of a received data available interrupt, writing to the Transmitter Holding Register if it was a THRE interrupt, or printing an error message in the case of a line status interrupt.

### **The GPIB-COM Controller Function**

Because most serial port applications involve communication with only one serial line, the GPIB-COM imposes some restrictions on the GPIB in order to be compatible with existing serial port software. The GPIB-COM must be System Controller of the GPIB and will not work with other Controllers. The behavior of the GPIB-COM depends on the setting of the talk-only jumper.